# RAIO RA8875

# Character/Graphic TFT LCD Controller

**Specification**

Version 2.1

April 11, 2016

RAiO Technology Inc.

©Copyright RAiO Technology Inc. 2011, 2012, 2013, 2014, 2015, 2016

|         | Update History    |                                                                                                                                                                                                  |  |  |  |

|---------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Version | Date Description  |                                                                                                                                                                                                  |  |  |  |

| 1.0     | May 10, 2011      | Preliminary Version                                                                                                                                                                              |  |  |  |

|         | June 15, 2011     | Remove Serial Flash Address 32 bit Mode 1. Modify REG[05h] 2. Remove REG [B3h] 3. Modify REG[E1h] 4. Modify Section 7-10-1 : DMA In Continuous Mode 5. Modify Section 7-10-2 : DMA In Block Mode |  |  |  |

| 1.1     | June 27, 2011     | 1. Modify REG[16h] \ REG[89h] \ REG[F0h]                                                                                                                                                         |  |  |  |

|         | October 4, 2011   | 1. Modify Figure 7-80 \ Figure 7-81                                                                                                                                                              |  |  |  |

|         | November 18, 2011 | <ol> <li>Modify Section 7-4-2</li> <li>Modify Table 8-2</li> </ol>                                                                                                                               |  |  |  |

|         | November 29, 2011 | <ol> <li>Add Figure 7-82</li> <li>Modify Figure 6-41</li> </ol>                                                                                                                                  |  |  |  |

| 1.2     | January 10, 2012  | 1. Modify Section 7-6 BTE Function (Parallel MCU interface only)                                                                                                                                 |  |  |  |

|         | February 10, 2012 | Add Appendix A                                                                                                                                                                                   |  |  |  |

| 1.3     | February 22, 2012 | 1. Modify REG[21h]                                                                                                                                                                               |  |  |  |

| 1.5     | March 16, 2012    | <ol> <li>Modify Section 4-8: pin description of OSC_VDD</li> <li>Modify Section 6-1-2: Serial I/F Protocol</li> <li>Add Note of REG[94h], REG[98h], Figure 7-29, Figure 7-30</li> </ol>          |  |  |  |

|         | May 15, 2012      | <ol> <li>Modify Section 5-2 : the Bit 1 of REG[01h]</li> <li>Modify Table 7-8</li> </ol>                                                                                                         |  |  |  |

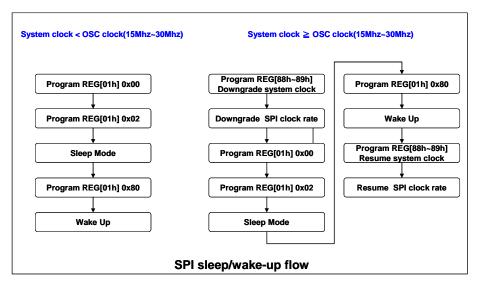

| 1.4     | March 27, 2013    | <ol> <li>Modify Section 4-1 : pin description of PS</li> <li>Modify Section 5-2 : REG[01h] \ REG[16h]</li> <li>Add Section 6-1-2-3 :SPI Sleep/Wake Up</li> </ol>                                 |  |  |  |

| 1.5     | May 3, 2013       | Modify Section 6-1-2-1 : 3-Wire SPI Interface     Modify Section 6-1-2-2 : 4-Wire SPI Interface                                                                                                  |  |  |  |

|         | June 18, 2013     | 1. Modify Figure 6-12 · Figure 6-18                                                                                                                                                              |  |  |  |

| 1.6     | July 17, 2013     | Modify Section 6-8 : Example of formula for system clock                                                                                                                                         |  |  |  |

|         | July 31, 2013     | 1. Modify Section 5-2 : REG[15h]                                                                                                                                                                 |  |  |  |

| 1.7     | December 03, 2013 | 1. Modify Figure 6-37~Figure 6-40 \ Figure 6-48                                                                                                                                                  |  |  |  |

| 1.8     | March 7, 2014     | 1. Modify Section 7-2-4 and Section 5-5 :REG[41h]                                                                                                                                                |  |  |  |

|         | May 29, 2014      | 1. Add Note 3 of Table 8-2                                                                                                                                                                       |  |  |  |

| 1.9     | August 11, 2014   | 1. Modify Section 4-3: PDAT[15:0]                                                                                                                                                                |  |  |  |

|         | October 16, 2014  | 1. Modify Table 7-23 & Table 7-24                                                                                                                                                                |  |  |  |

| 2.0     | December 11, 2014 | 1. Add REG[02h] description in BTE flow step for write/read data (7-6-4-1,7-6-4-2,7-6-4-5,7-6-4-9,7-6-4-10)                                                                                      |  |  |  |

| 2.1     | April 11, 2016    | 1. Add Figure 6-27 \ Figure 6-29 \ Figure 6-31                                                                                                                                                   |  |  |  |

| Ch     | apte | r Contents                                      | Page |

|--------|------|-------------------------------------------------|------|

| <br>1. | Des  | scription                                       | 7    |

|        |      | tures                                           |      |

|        |      |                                                 |      |

| 3.     |      | ck Diagram                                      |      |

|        | 3-1  | Block Diagram                                   |      |

|        | 3-2  | System Block Diagram                            |      |

| 4.     | Pin  | Description                                     | 9    |

|        | 4-1  | MCU Interface                                   | 9    |

|        | 4-2  | Serial MCU Interface                            | 10   |

|        | 4-3  | LCD Panel Interface                             | 10   |

|        | 4-4  | Serial Flash/ROM Interface                      | 11   |

|        | 4-5  | Touch Interface                                 | 11   |

|        | 4-6  | KEYSCAN Interface                               | 11   |

|        | 4-7  | PWM Interface                                   | 12   |

|        | 4-8  | Clock and Power Interface                       | 12   |

| 5.     | Reg  | jister                                          | 13   |

|        | 5-1  | Status Register                                 | 14   |

|        | 5-2  | System & Configuration Registers                | 14   |

|        | 5-3  | LCD Display Control Registers                   |      |

|        | 5-4  | Active Window & Scroll Window Setting Registers |      |

|        | 5-5  | Cursor Setting Registers                        |      |

|        | 5-6  | Block Transfer Engine(BTE) Control Registers    | 30   |

|        | 5-7  | Touch Panel Control Registers                   |      |

|        | 5-8  | Graphic Cursor Setting Registers                | 38   |

|        | 5-9  | PLL Setting Registers                           | 39   |

|        | 5-10 | PWM Control Registers                           | 40   |

|        | 5-11 | Drawing Control Registers                       | 42   |

|        |      | DMA Registers                                   |      |

|        | 5-13 | Key & IO Control Registers                      | 50   |

|        | 5-14 | Floating Window Control Registers               | 51   |

|        |      | Serial Flash Control Registers                  |      |

|        |      | Interrupt Control Registers                     |      |

| 6.     |      | dware Interfaced                                |      |

|        | 6-1  | MCU Interface                                   | 56   |

|        | •    | 6-1-1 Protocol                                  |      |

|        |      | 6-1-1-1 Parallel I/F Protocol                   |      |

|        | •    | 6-1-2 Serial I/F Protocol                       |      |

|        |      | 6-1-2-2 4-Wire SPI Interface                    |      |

|        |      | 6-1-2-3 SPI Sleen / Wake I In                   | 66   |

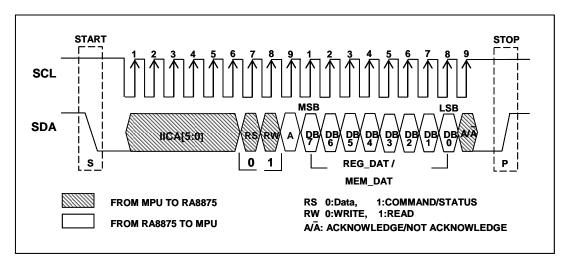

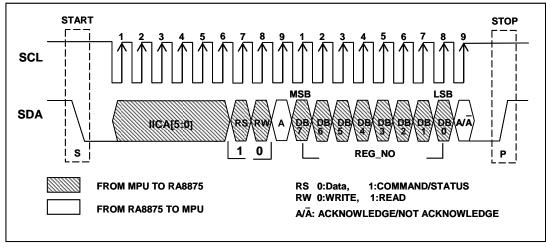

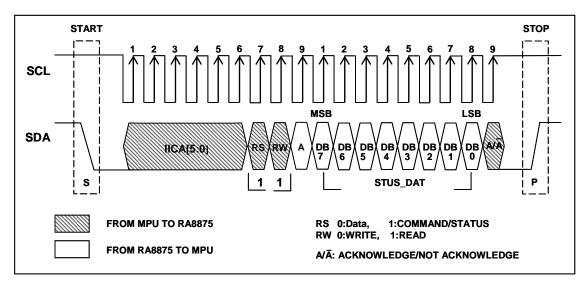

|    | 6-1-2-4 IIC I/F                                          |    |

|----|----------------------------------------------------------|----|

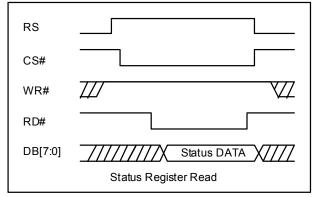

|    | 6-1-3 Read Status Register                               | 69 |

|    | 6-1-4 Write Command to Register                          | 70 |

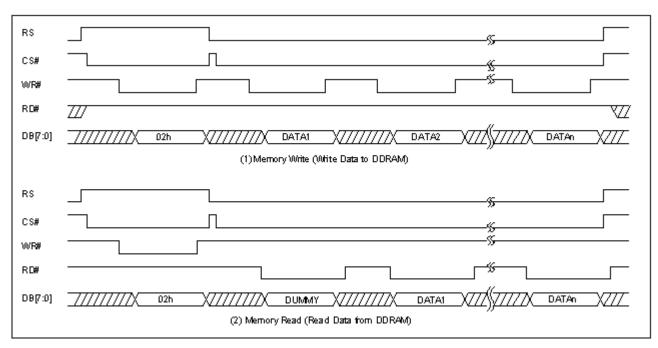

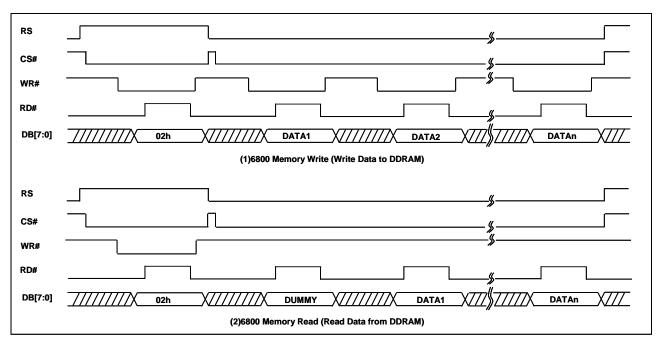

|    | 6-1-5 Memory Read / Write Operation                      | 72 |

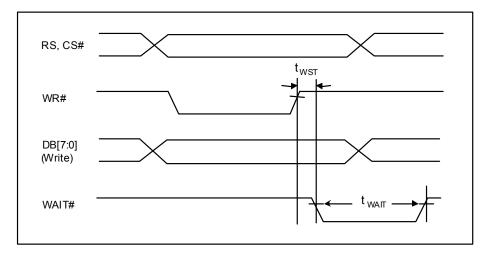

|    | 6-1-6 Interrupt and Wait                                 | 74 |

|    | 6-1-6-1 Interrupt                                        |    |

|    | 6-1-6-2 Wait                                             |    |

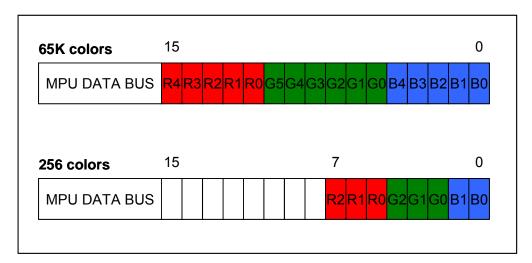

|    | 6-1-7 Data Format                                        |    |

|    | 6-1-7-1 MCU Data Bus 16- Bit                             |    |

|    | 6-1-7-2 MCU Data Bus 8-Bit                               |    |

|    | 6-2 Driver I/F Color Setting Mode                        | 78 |

|    | 6-3 LCD Interface                                        | 79 |

|    | 6-4 External Serial Flash/ROM                            | 81 |

|    | 6-4-1 External Serial Font ROM                           | 84 |

|    | 6-4-2 External Serial Data ROM                           | 85 |

|    | 6-5 Touch Panel I/F                                      | 86 |

|    | 6-6 KEYSCAN                                              |    |

|    |                                                          |    |

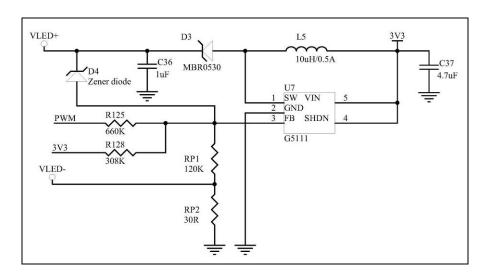

|    | 6-7 PWM                                                  |    |

|    | 6-8 Clock and PLL                                        |    |

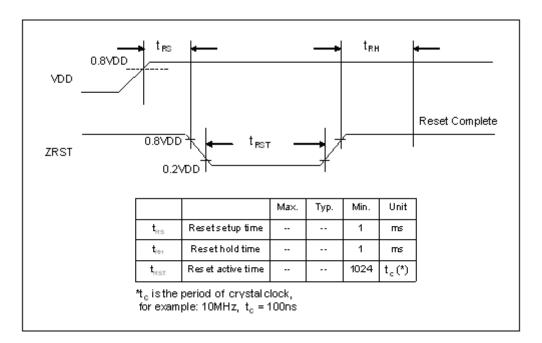

|    | 6-9 Reset                                                | 92 |

|    | 6-10 Power                                               | 94 |

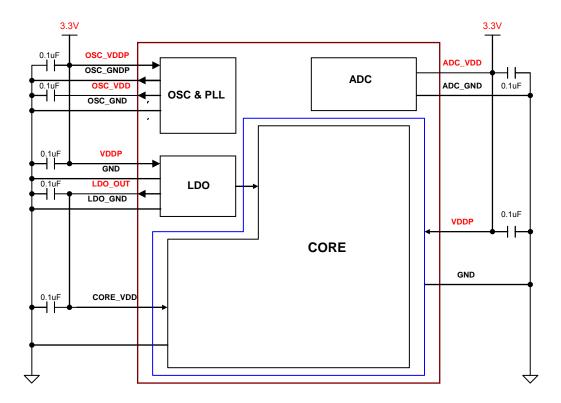

|    | 6-10-1 Power Pin Description                             | 94 |

|    | 6-10-2 Power Architecture                                | 94 |

| 7. | 7. Function Description                                  | 95 |

|    | 7-1 Scroll Function                                      |    |

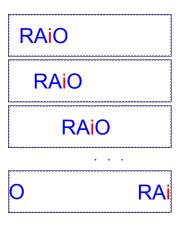

|    | 7-1-1 Scroll Window & Scroll Offset                      |    |

|    | 7-1-2 Horizontal Scroll & Vertical Scroll                |    |

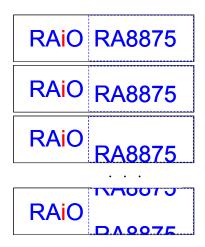

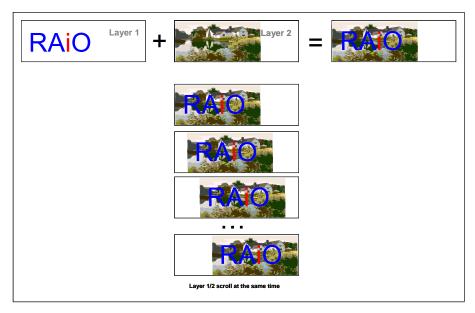

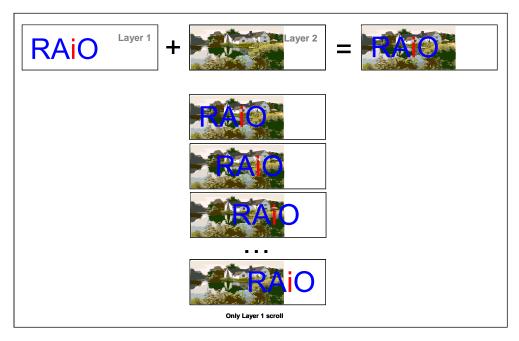

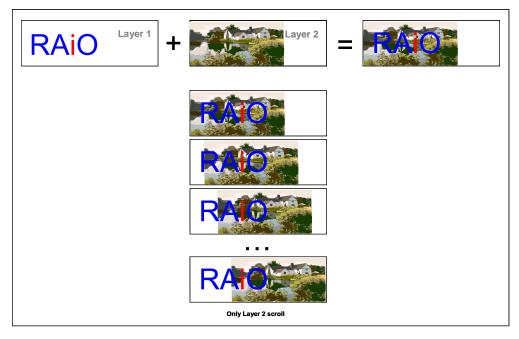

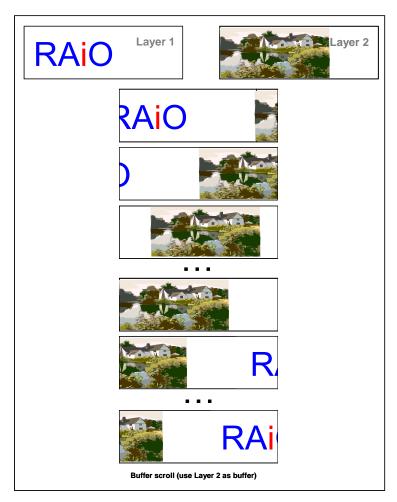

|    | 7-1-3 Layer Mixed Scroll                                 |    |

|    | 7-1-3-1 Layer 1/2 Scroll Simultaneously                  |    |

|    | 7-1-3-2 Only Layer 1 Scroll                              |    |

|    | 7-1-3-3 Only Layer 2 Scroll                              |    |

|    | 7-1-3-4 Buffer Scroll (Layer 2 is used as Scroll Buffer) |    |

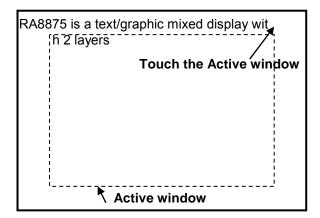

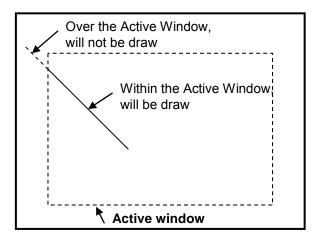

|    | 7-2 Active Window                                        |    |

|    | 7-2-1 Active Window for Font Write                       |    |

|    | 7-2-1 Active Window for Geometric Input                  |    |

|    | 7-2-3 Active Window for DMA                              |    |

|    | 7-2-4 Active Window for Memory Write                     |    |

|    | 7-3 Cursor & Pattern                                     |    |

|    | 7-3-1 Cursor Type                                        |    |

|    | 7-3-1                                                    |    |

|    | 7-3-1-1 Graphic Cursor                                   |    |

|    | 7-3-1-3 Memory Write Cursor                              |    |

|    | 7-3-1-4 Font Write Cursor                                |    |

|    | 7-3-2 Cursor Attribute                                   |    |

|    | 7-3-2-1 Cursor Blinking                                  |    |

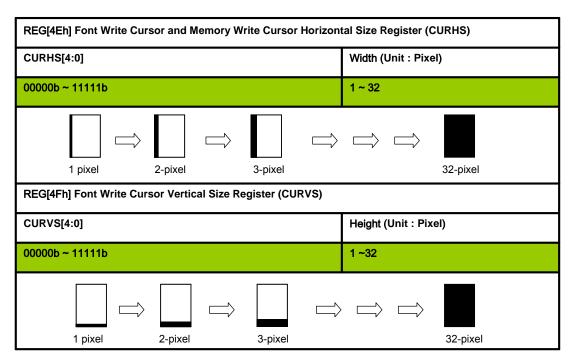

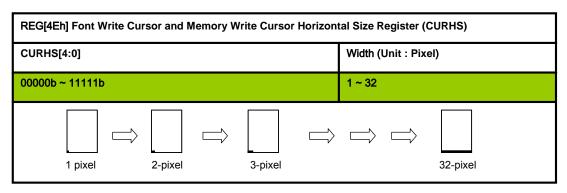

|    | 7-3-2-2 Cursor Height and Width                          |    |

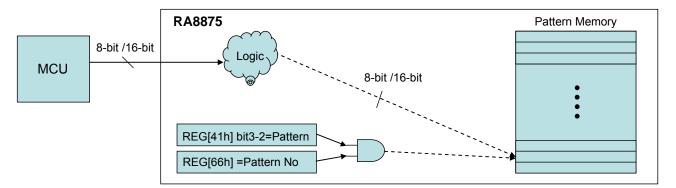

|    | 7-3-3 Pattern                                            |    |

|    | 7-4 Font                                                 |    |

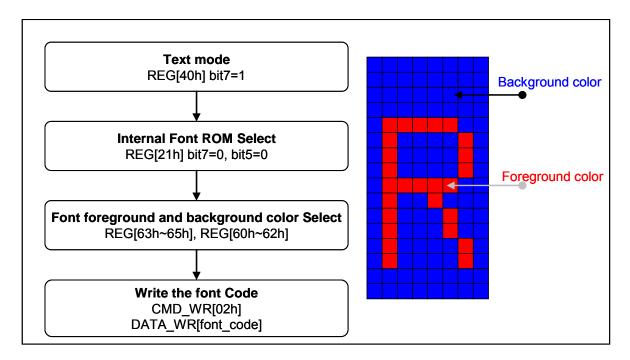

|    | 7-4-1 Internal Font ROM                                  |    |

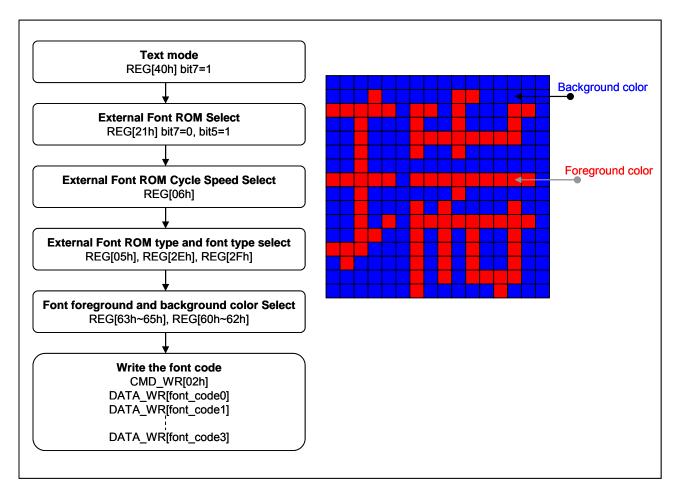

|     | 7-4-2          | Exter  | nal Font ROM                                   | 114 |

|-----|----------------|--------|------------------------------------------------|-----|

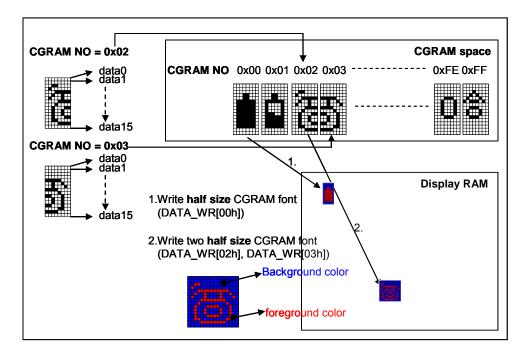

|     | 7-4-3          | CGRA   |                                                | 115 |

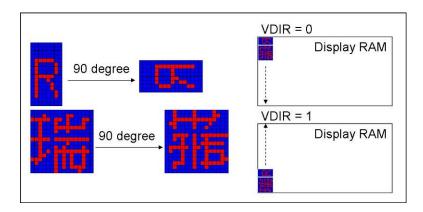

|     | 7-4-4          | 90 De  | gree Font                                      | 117 |

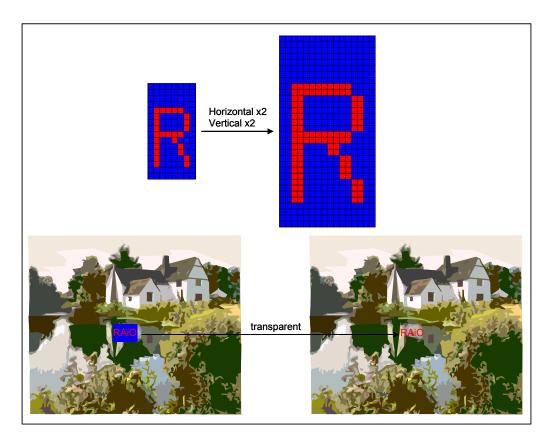

|     | 7-4-5          | Enlar  | gement, Transparent Font                       | 117 |

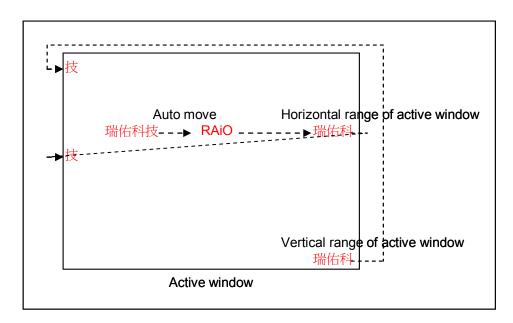

|     | 7-4-6          | Font ( | Change Line when Setting Write Auto Move       | 118 |

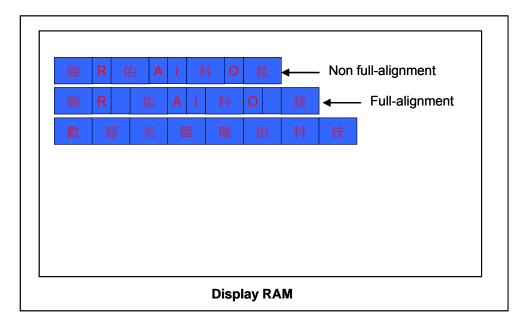

|     |                |        | Full-Alignment                                 |     |

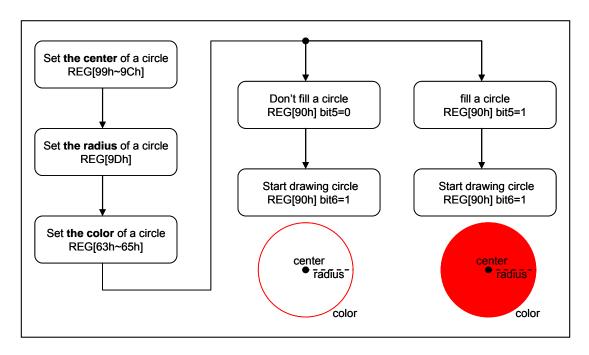

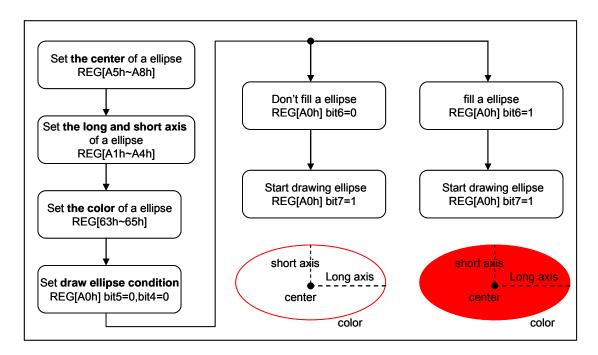

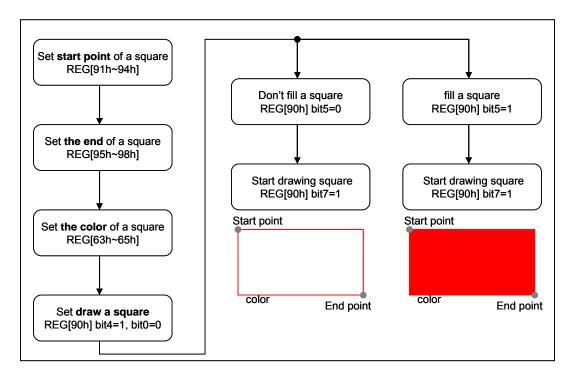

| 7-5 |                |        | ic Pattern Drawing Engine                      |     |

| . 0 |                |        | Input                                          |     |

|     |                |        | e Input                                        |     |

|     |                | •      | e Input                                        |     |

|     |                |        | re Input                                       |     |

|     |                | •      | nputnput                                       |     |

|     |                |        | gle Input                                      |     |

|     |                |        |                                                |     |

|     |                | _      | re Of Circle Corner Input                      |     |

| 7-6 |                | -      | ck Transfer Engine) Function                   |     |

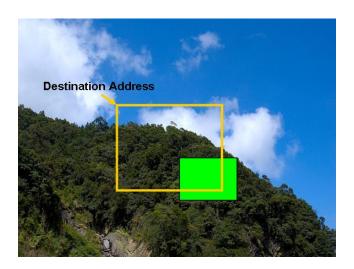

|     |                |        | t BTE Start Point Address and Layer            |     |

|     | 7-6-2          | BTE (  | Operations                                     |     |

|     | 7-6            | 6-2-1  | Write BTE                                      |     |

|     | 7-6            | 6-2-2  | Read BTE                                       |     |

|     | 7-6            | 6-2-3  | Move BTE                                       |     |

|     | 7-6            | 3-2-4  | Solid Fill                                     | 129 |

|     | 7-6            | 3-2-5  | Pattern Fill                                   | 129 |

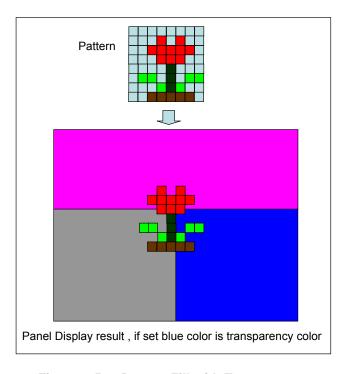

|     | 7-6            | 6-2-6  | Transparent Pattern Fill                       | 129 |

|     | 7-6            | 6-2-7  | Transparent Write BTE                          | 129 |

|     | 7-6            | 6-2-8  | Transparent Move BTE                           | 129 |

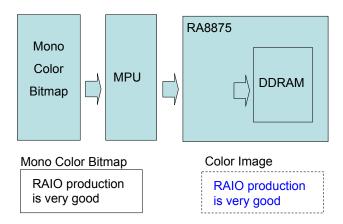

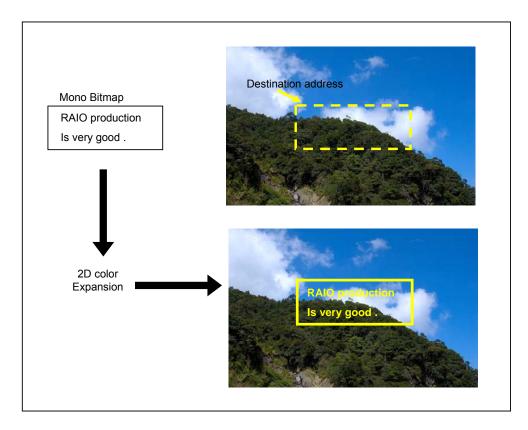

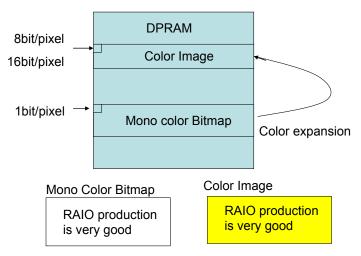

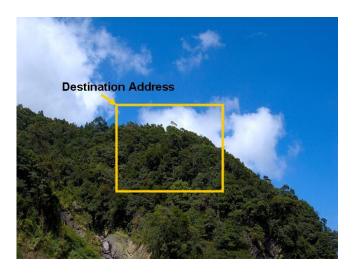

|     | 7-6            | 3-2-9  | Color Expansion                                | 130 |

|     | 7-6            | 3-2-10 | Move BTE with Color Expansion                  | 130 |

|     | 7-6-3          | BTE A  | Access Memory Method                           | 131 |

|     | 7-6            | 3-3-1  | Block Memory Access                            | 131 |

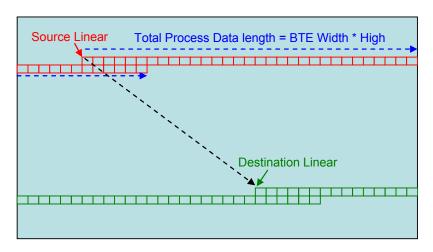

|     | 7-6            | 3-3-2  | Linear Memory Access                           | 131 |

|     | 7-6-4          | BTE F  | unction Explaination                           | 132 |

|     | 7-6            | 3-4-1  | Write BTE with ROP                             | 132 |

|     | 7-6            | 6-4-2  | Read BTE (Burst Read Like Function)            | 134 |

|     | 7-6            | 3-4-3  | Move BTE in Positive Direction with ROP        | 135 |

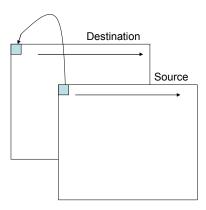

|     | 7-6            | 3-4-4  | Move BTE in Negative Direction with ROP        | 136 |

|     | 7-6            | 3-4-5  | Transparent Write BTE                          | 138 |

|     | 7-6            | 6-4-6  | Transparent Move BTE Positive Direction        |     |

|     | 7-6            | 6-4-7  | Pattern Fill with ROP                          | 141 |

|     | 7-6            | 6-4-8  | Pattern Fill with Transparency                 | 143 |

|     | 7-6            | 6-4-9  | Color Expansion                                |     |

|     | 7-6            | 6-4-10 | Color Expansion with Transparency              | 148 |

|     | 7-6            | 6-4-11 | Move BTE with Color Expansion                  |     |

|     |                |        | Move BTE with Color Expansion and Transparency |     |

|     |                |        | Solid Fill                                     |     |

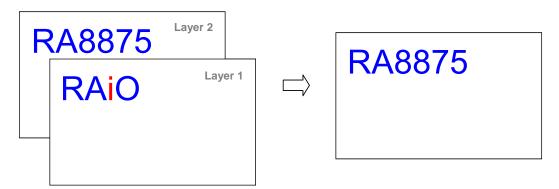

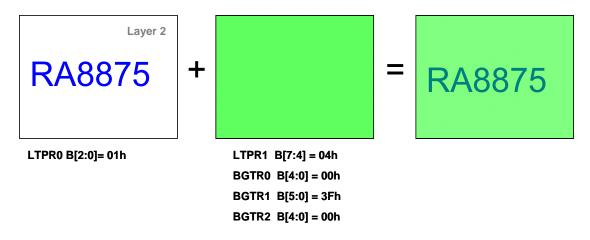

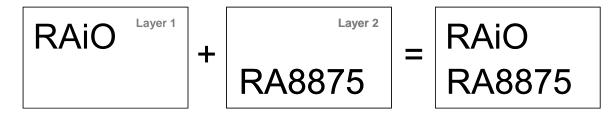

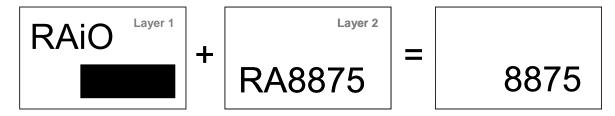

| 7-7 |                |        | xed Function                                   |     |

|     |                |        | Layer One is Visible                           |     |

|     | 7-7-1<br>7-7-2 | -      | Layer One is Visible                           |     |

|     |                | -      | · ·                                            |     |

|     |                | _      | en-Overlay Mode                                |     |

|     |                |        | parent Mode                                    |     |

|     |                |        | an OR                                          |     |

|     |                |        | an AND                                         |     |

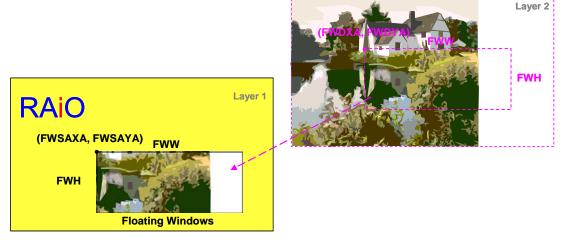

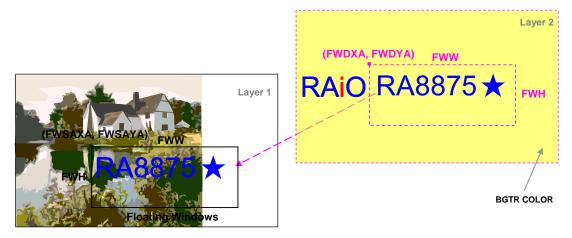

|     | <i>(-/-/</i>   | rioati | ng Window                                      | 158 |

| 7-8 Touch Panel Function              | 159                              |

|---------------------------------------|----------------------------------|

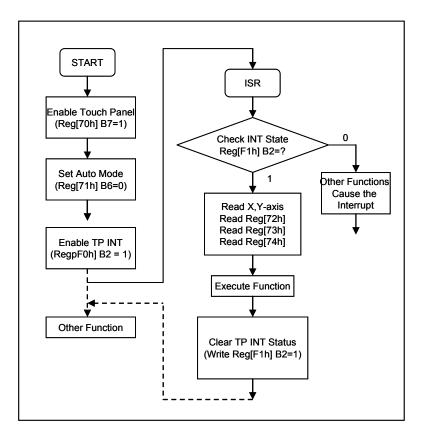

| 7-8-1 Touch Panel Operation Mode      | 160                              |

| 7-8-1-1 Auto Mode                     | 160                              |

| 7-8-1-2 Manual Mode                   | 161                              |

| 7-8-2 Touch Event Detection Modes     | 162                              |

| •                                     | 162                              |

|                                       | 162                              |

| 7-8-3 Touch Panel Sampling Time Refer | ence Table163                    |

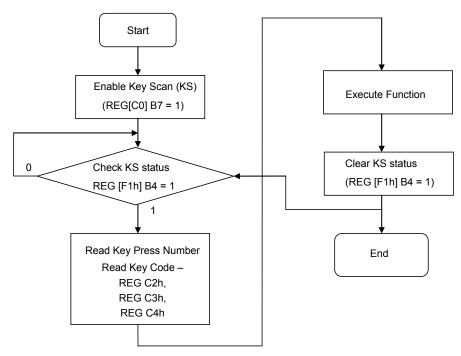

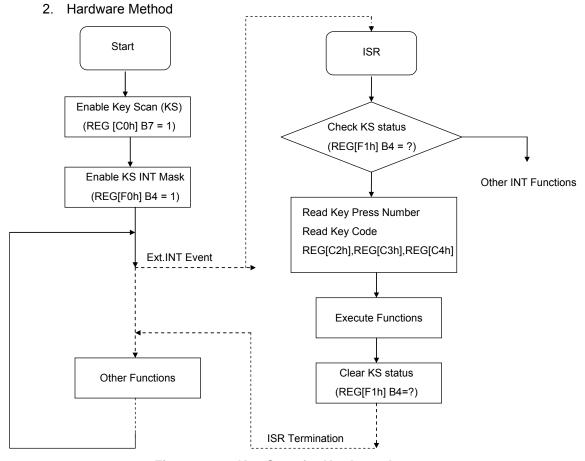

| 7-9 KEYSCAN                           |                                  |

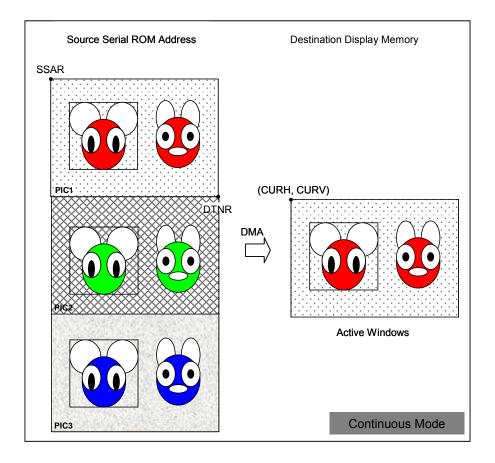

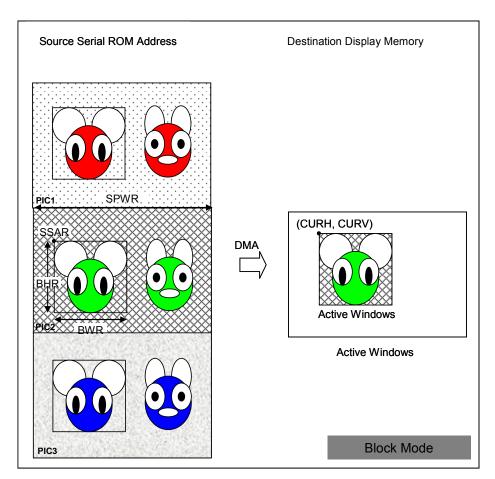

| 7-10 DMA (Direct Memory Access)       |                                  |

|                                       | 167                              |

|                                       | 169                              |

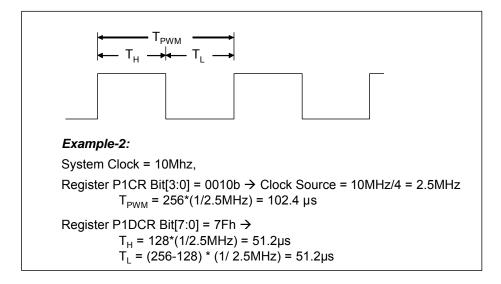

| 7-11 PWM                              | 170                              |

|                                       | 171                              |

| 8. AC/DC Characteristic               | 173                              |

| 8-1 Maximum Absolute Limit            | 173                              |

| 8-2 DC Characteristic                 | 174                              |

| 9. Package                            | 175                              |

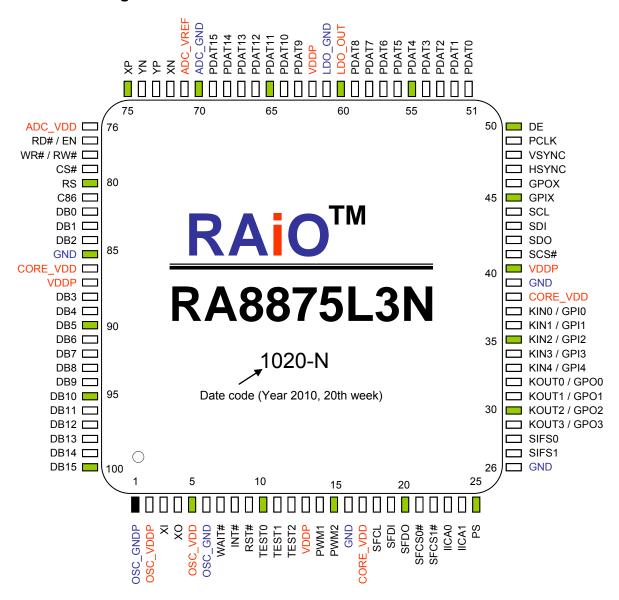

| 9-1 Pin Assignment                    | 175                              |

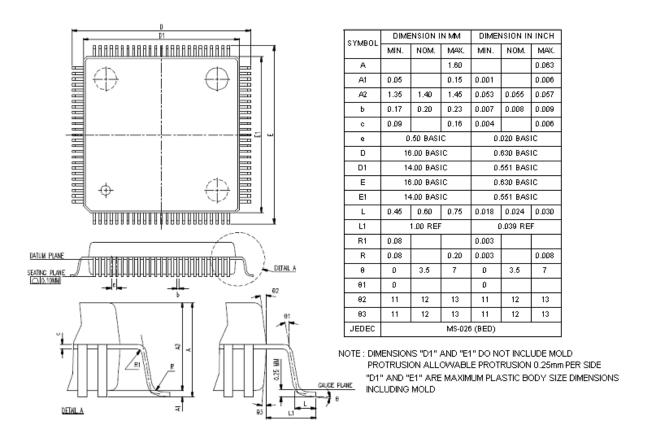

| 9-2 Package Outline Dimensions        |                                  |

| 9-3 Product Number                    | 176                              |

| Appendix A. Summary for GENIT         | OP's Font Supported by RA8875177 |

#### 1. Description

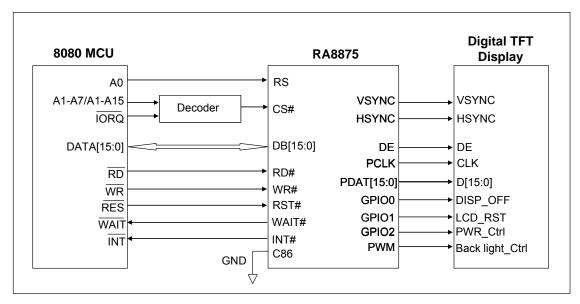

RA8875 is a text/graphic mixed display with 2 layers TFT LCD controller. It is designed to meet the requirement of middle size TFT module up to 800x480 pixels with characters or 2D graphic application. Embedded 768KB display RAM provides user a flexible solution for display buffer of almost application. Besides, the interface of external serial flash is optional to provide the font bitmap up to 32x32 pixels for BIG5/GB/UNICODE coding, by connecting with the font ROM of Genitop Inc. For graphic usage, RA8875 supports a 2D Block Transfer Engine(BTE) that is compatible with 2D BitBLT function for processing the mass data transfer. The advanced geometric speed-up engine provides user an easy way to draw the programmable geometric shapes by hardware, like line, square, circle and ellipse. Besides, for different end-user applications, many powerful functions are integrated with RA8875, such as scroll function, floating window display, graphic pattern and font enlargement function. These functions will save user a large of software effort during development period.

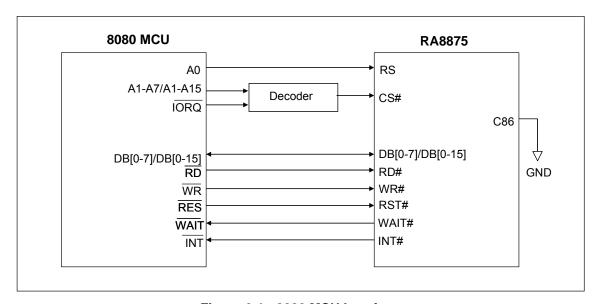

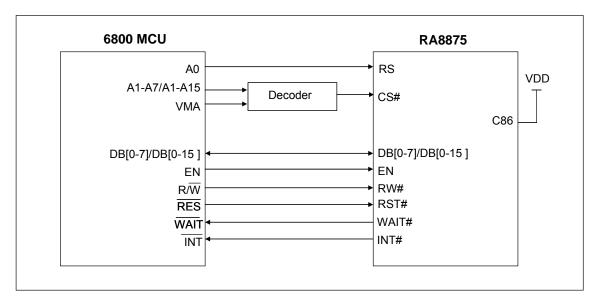

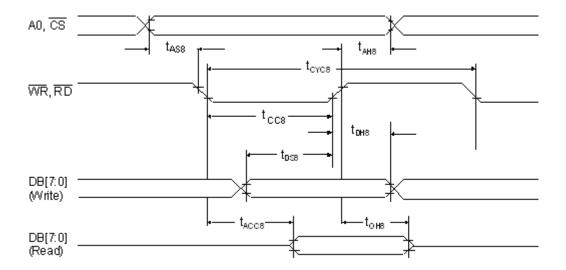

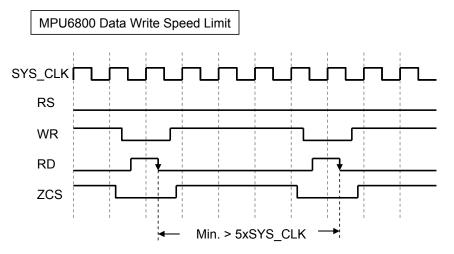

RA8875 is a powerful and cheap choice for color display application. To reduce the system cost, RA8875 provides low cost and easy-to-use 8080/6800 parallel MCU interface. Because of the powerful hardware speed-up function embedded in it, less data transfer is needed so more efficiency is improved, RA8875 also provides serial SPI/I2C I/F with ultra-low pin-count. Useful device controller, such as flexible 4-wire touch panel controller, PWM for adjusting panel back-light are also included to reduce the system cost for customer. With the RA8875 design-in, user can achieve an easy-to-use, low-cost and high performance system comparing with the other solution.

#### 2. Features

- Support Text/Graphic Mixed Display Mode.

- ◆ Embedded 768KB DDRAM.

- ◆ Color Depth TFT: 256/65K Colors.

- ◆ Supporting TFT 8/16 bpp Generic RGB Interface.

- ◆ Supporting TFT Panel Size:

- 800x480 Pixels 2 Layers @ 256 Colors.

- 800x480 Pixels 1 Layer @ 64K Colors.

- 480x272 Pixels 2 Layers @ 64K Colors.

- ◆ Supporting MCU Interface :

- 8080/6800 with 8/16 Data Bus Width

- I2C or 3/4-wire SPI I/F.

- Powerful Block Scrolling Function for Vertical or Horizontal Direction.

- ◆ Embedded 10KB Character ROM with Font Size 8x16 Dots and Supporting Character Sets of ISO/IEC 8859-1/2/3/4.

- External Serial Flash/ROM SPI I/F Supporting.

- ◆ Supporting Genitop Inc. UNICODE/BIG5/GB Serial font ROM with 16x16/24x24/32X32 dots Font Size.

- Font Enlargement Function X1, X2, X3, X4 for Horizontal/Vertical Direction.

- ◆ Font Vertical Rotation Mode Function.

- ◆ Block Transfer Engine (BTE) Supports with 2D Function, Compatible with 2D BitBLT Function.

- Embedded Geometric Speed-up Engine.

- Programmable Font Write Cursor for Writing with Character.

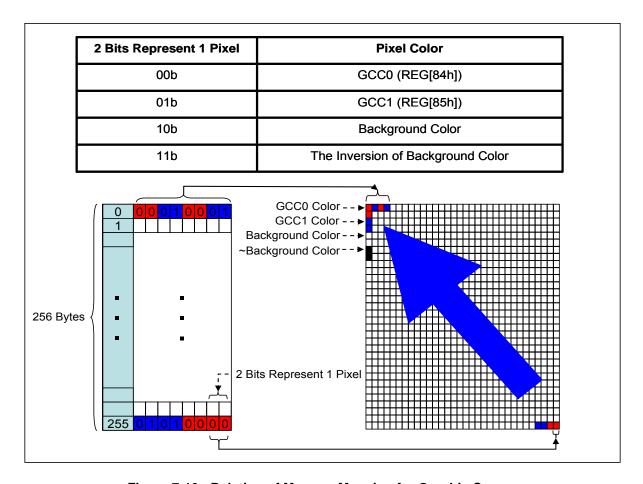

- ◆ 32x32 pixels Graphic Cursor Function.

- User-defined Characters.

- 256 Characters with 8x16 dots.

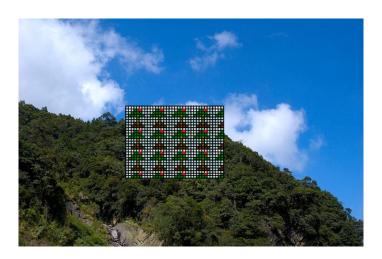

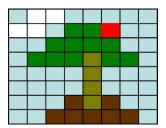

- Supporting 16 User-defined Patterns of 8x8 pixels, or 4 User-defined Pattern for 16x16 pixels.

- Two Programmable PWM for Back-Light Adjusting or other's Application.

- ◆ Embedded 4-wire Touch Panel Controller.

- ◆ Sleep Mode with Low Power Consumption.

- ◆ Embedded Smart 4x5 Key-Scan Controller.

- 4 Sets of Programmable GPO and a fixed GPOX.

- ◆ 5 Sets of Programmable GPI and a fixed GPIX

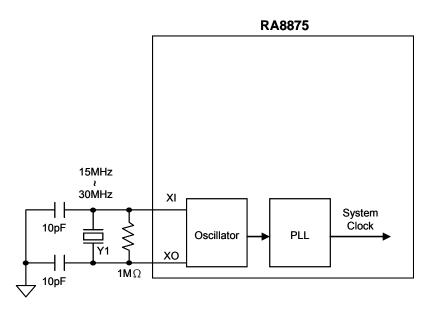

- Clock Source : Embedded Crystal Oscillator Circuit with Programmable PLL.

- ◆ Operation Voltage: 3.0V~3.6V.

- Package: LQFP-100pin.

# 3. Block Diagram

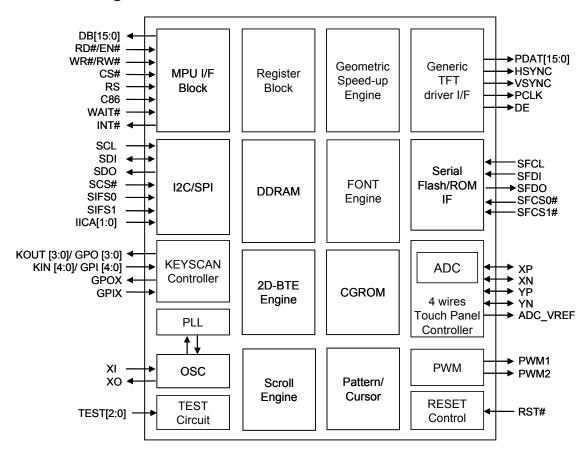

#### 3-1 Block Diagram

Figure 3-1: RA8875 Block Diagram

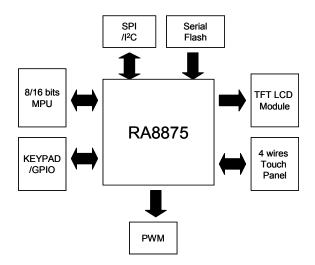

#### 3-2 System Block Diagram

Figure 3-2: RA8875 System Block Diagram

# 4. Pin Description

# 4-1 MCU Interface

| Pin Name     | I/O | Pin Description                                                                                                                                                                                                                                                                                                                                |  |  |

|--------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DB[15:0]     | Ю   | Data Bus These are data bus for data transfer between MCU and RA8875. When setting register number and register data, DB[7:0] is used. When writing data to display RAM, DB[15:0] is used according to data bus mode setting. DB[15:8] will be input and should be pull-low or pull-high when 8-bit data bus mode is used.                     |  |  |

| RD#<br>(EN)  | I   | Enable/Read Enable When MCU interface (I/F) is 8080 series, this pin is used as RD# signal (Data Read), active low. When MCU I/F is 6800 series, this pin is used as EN signal (Enable), active high.                                                                                                                                          |  |  |

| WR#<br>(RW#) | I   | Write/Read-Write When MCU I/F is 8080 series, this pin is used as WR# signal (data write), active low. When MCU I/F is 6800 series, this pin is used as RW# signal (data read/write control). Active high for read and active low for write.                                                                                                   |  |  |

| CS#          | 1   | Chip Select Input Low active chip select pin.                                                                                                                                                                                                                                                                                                  |  |  |

| RS           | I   | Command / Data Select Input The pin is used to select command/data cycle. RS = 0, data Read/Write cycle is selected. RS = 1, status read/command write cycle is selected. In 8080 interface, usually it connects to "A0" address pin.    RS   WR#   Access Cycle                                                                               |  |  |

| C86          | 1   | MCU Interface Select 0: 8080 interface is selected 1: 6800 interface is selected                                                                                                                                                                                                                                                               |  |  |

| PS           | I   | Parallel /Serial I/F Select Input  0: Parallel 8080/6800 I/F select  1: Serial 3/4-wire SPI or IIC I/F select.  PS input is used to select the active MCU interface, it must be set correctly before the command /data cycle asserting. We also recommend that DB[15:0], RD#(EN), WR#(RW#), CS#,RS and C86 pin tie high when using serial I/F. |  |  |

| INT#         | 0   | Interrupt Signal Output The interrupt output for MCU to indicate the status of RA8875.                                                                                                                                                                                                                                                         |  |  |

| WAIT#        | 0   | Wait Signal Output This is a WAIT# output to indicate the RA8875 is in busy state. The RA8875 can't access MCU cycle when WAIT# pin is active. It is active low and could be used for MCU to poll busy status by connecting it to I/O port.                                                                                                    |  |  |

# 4-2 Serial MCU Interface

| Pin Name  | I/O | Pin Description                                                                                                                                                                                                     |  |

|-----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SCL       | I   | SPI Clock 3-wire, 4-wire Serial or IIC I/F clock. If no use, please connect it to VDDP.                                                                                                                             |  |

| SDI       | I/O | IIC data /4-wire SPI Data Input 4-wire SPI I/F: Data input for serial I/F. 3-wire SPI I/F: NC, please connect it to VDDP. IIC I/F: Bi-direction data for serial I/F If no use, please connect it to VDDP.           |  |

| SDO       | I/O | 3-wire SPI Data /4-wire SPI Data Output 4-wire SPI I/F: Data output for serial I/F. 3-wire SPI I/F: Bi-direction data for serial I/F IIC I/F: NC, if no use, please keep floating. If no use, please keep floating. |  |

| SCS#      | _   | SPI Chip Select Chip select pin for 3-wire or 4-wire serial I/F. IIC I/F: NC, please connect it to VDDP. If no use, please connect it to VDDP.                                                                      |  |

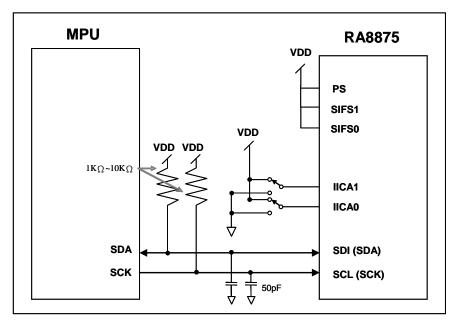

| IICA[1:0] | ı   | IIC I/F: IIC Address Select. Other I/F: NC, please don't keep floating.                                                                                                                                             |  |

| SIFS[1:0] | I   | Serial Interface Selection 00 : NC. 01 : 3-Wire SPI 10 : 4-Wire SPI 11 : IIC If serial I/F is no use, please connect them to 00.                                                                                    |  |

## 4-3 LCD Panel Interface

| Pin Name   | I/O            | Pin Description                                                                                                                                                                                                                  |                               |            |           |  |

|------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------|-----------|--|

|            |                | LCD Panel Data Bus TFT LCD data bus output for source driver. RA8875 supports 256/64K color depth by register (REG[10h]), user can connect corresponding RGB bus for different setting. For unused pin please keeps it floating. |                               |            |           |  |

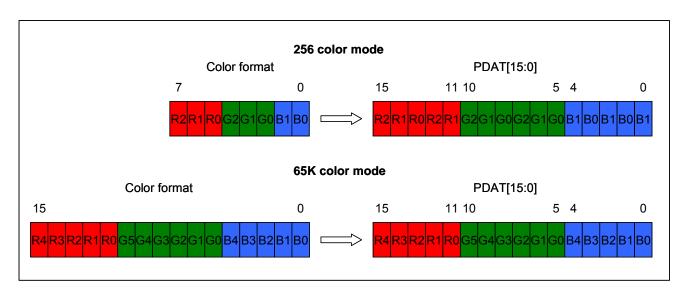

| PDAT[15:0] | 0              | Color Depth                                                                                                                                                                                                                      | Red                           | Green      | Blue      |  |

|            |                | 256                                                                                                                                                                                                                              | PDAT[15:13]                   | PDAT[10:8] | PDAT[4:3] |  |

|            |                | 64K                                                                                                                                                                                                                              | PDAT[15:11]                   | PDAT[10:5] | PDAT[4:0] |  |

|            |                |                                                                                                                                                                                                                                  |                               |            |           |  |

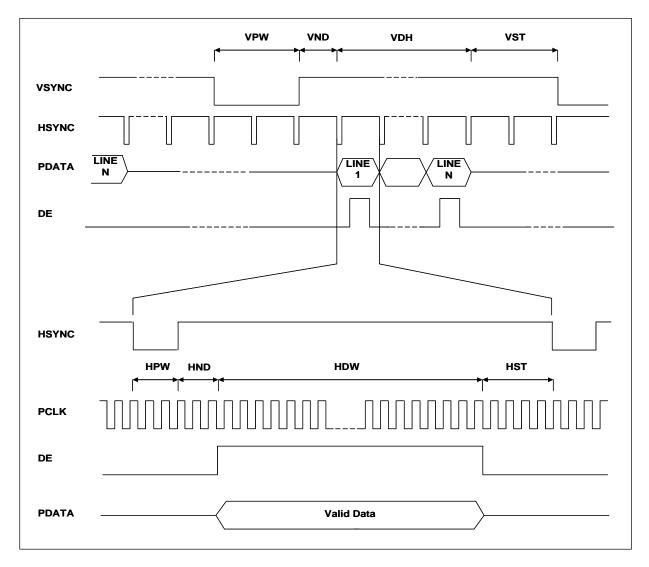

| HSYNC      | 0              | HSYNC Pulse Generic TFT interface signal.                                                                                                                                                                                        |                               |            |           |  |

|            | _              | VSYNC Pulse                                                                                                                                                                                                                      | acc signal.                   |            |           |  |

| VSYNC      | <b>VSYNC</b> O |                                                                                                                                                                                                                                  | Generic TFT interface signal. |            |           |  |

| PCLK       | 0              | Pixel Clock Generic TFT interface signal.                                                                                                                                                                                        |                               |            |           |  |

| DE         | 0              | Data Enable Generic TFT interface signal.                                                                                                                                                                                        |                               |            |           |  |

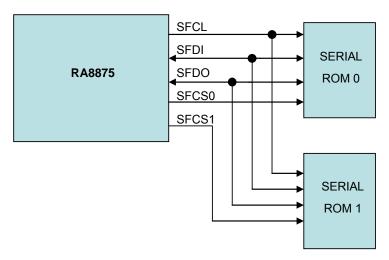

# 4-4 Serial Flash/ROM Interface

| Pin Name  | I/O | Pin Description                                                                                                                                                                          |  |

|-----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SFCL      | 0   | External Serial Flash/ROM Clock Serial Flash/ROM SPI I/F clock.                                                                                                                          |  |

| SFDI/SIO0 | I/O | External Flash/ROM SPI Data Input Single mode: Data input of serial Flash/ROM SPI I/F. For RA8875, it is output (Default). Dual mode: The signal is used as bi-direction data #0(SIO0).  |  |

| SFDO/SIO1 | I/O | External Flash/ROM SPI Data Output Single mode: Data output of serial Flash/ROM SPI I/F. For RA8875, it is input (Default). Dual mode: The signal is used as bi-direction data #1(SIO1). |  |

| SFCS0#    | 0   | External Flash/ROM SPI Chip Select 0 Chip select pin for serial Flash/ROM SPI I/F #0.                                                                                                    |  |

| SFCS1#    | 0   | External Flash/ROM SPI Chip Select 1 Chip select pin for serial Flash/ROM SPI I/F #1.                                                                                                    |  |

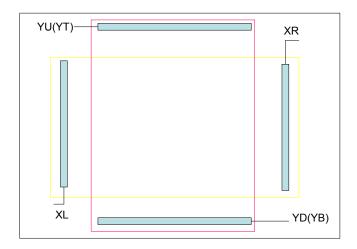

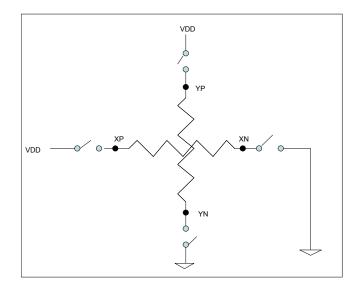

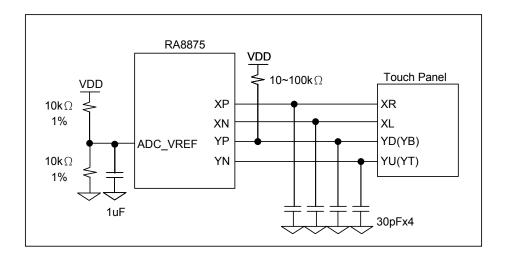

#### 4-5 Touch Interface

| Pin Name | I/O | Pin Description                                                                                                                                                       |  |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| YN       | Α   | YN Signal for Touch Panel 4-wire TP YN Control Signal.                                                                                                                |  |

| YP       | Α   | YP Signal for Touch Panel 4-wire TP YP Control Signal.                                                                                                                |  |

| XN       | Α   | XN Signal for Touch Panel 4-wire TP XN Control Signal.                                                                                                                |  |

| XP       | Α   | XP Signal for Touch Panel 4-wire TP XP Control Signal.                                                                                                                |  |

| ADC_VREF | А   | TP ADC Reference Voltage This pin is the reference voltage for ADC as 0.5*VDD. The reference voltage could be generated by RA8875 (default) or from external circuit. |  |

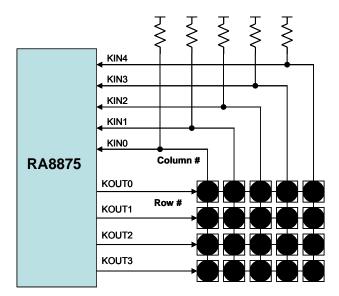

# 4-6 KEYSCAN Interface

| Pin Name                 | I/O | Pin Description                                                                                                                                                                                              |

|--------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KOUT[3:0]/<br>(GPO[3:0]) | 0   | Keypad Strobe Line or GPOs (General Purpose Output) Keypad matrix strobe lines outputs with open-drain. (Default). They could be programmed as GPOs by register setting, if don't use, please keep floating. |

| KIN[4:0]/<br>(GPI[4:0])  | I   | Keypad Data Line or GPIs (General Purpose Input) Keypad data inputs (Default), please add pull-up resister. They could be programmed as GPIs by register setting, if don't use, please connect it to GND.    |

| GPOX                     | 0   | Extra GPO (General Purpose Output) Additional GPO signal, if don't use, please keep floating.                                                                                                                |

| GPIX                     | I   | Extra GPI (General Purpose Input) Additional GPI signal, if don't use, please connect it to GND.                                                                                                             |

#### 4-7 PWM Interface

| Pin Name | I/O | Pin Description     |  |

|----------|-----|---------------------|--|

| PWM1     | 0   | PWM signal output 1 |  |

| PWM2     | 0   | PWM signal output 2 |  |

#### 4-8 Clock and Power Interface

| Pin Name  | I/O | Pin Description                                                                                                                                                                                                                                       |

|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ΧI        | I   | Crystal Input Pin Input pin for internal crystal circuit. It should be connected to external crystal circuit. That will generate the system clock for RA8875.                                                                                         |

| хо        | 0   | Crystal Output Pin Output pin for internal crystal circuit. It should be connected to external crystal circuit. That will generate the system clock for RA8875.                                                                                       |

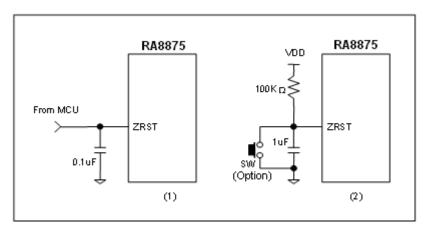

| RST#      | I   | Reset Signal Input This active-low input performs a hardware reset on the RA8875. It is a Schmitt-trigger input with pull-up resistor for enhanced noise immunity; however, it must ensure that it is not triggered if the supply voltage is too low. |

| TEST[2:0] | I   | <b>Test Mode Input</b> For chip test function, should be connected to GND for normal operation.                                                                                                                                                       |

| VDDP      | Р   | IO VDD<br>3.3V IO power input.                                                                                                                                                                                                                        |

| CORE_VDD  | Р   | CORE VDD  1.8 V Core power input.                                                                                                                                                                                                                     |

| LDO_OUT   | Р   | LDO VDD Output  1.8V power generated by internal LDO. It must connect bypass capacities to prevent power noise.                                                                                                                                       |

| LDO_GND   | Р   | LDO GND Ground signal for internal LDO.                                                                                                                                                                                                               |

| OSC_VDDP  | Р   | OSC IO VDD The separated OSC 3.3V IO power.                                                                                                                                                                                                           |

| OSC_VDD   | Р   | OSC VDD OSC 1.8 V power output. It is used by OSC core. It is suggested to connect the bypass capacitor nearby the pad.                                                                                                                               |

| OSC_GNDP  | Р   | OSC IO GND The separated OSC IO ground signal.                                                                                                                                                                                                        |

| OSC_GND   | Р   | OSC GND OSC ground signal and are internally connected to OSC_GNDP.                                                                                                                                                                                   |

| ADC_VDD   | Р   | ADC VDD ADC 3.3V power signal.                                                                                                                                                                                                                        |

| ADC_GND   | Р   | ADC GND ADC ground signal                                                                                                                                                                                                                             |

| GND       | Р   | GND IO Cell/Core ground signal                                                                                                                                                                                                                        |

## 5. Register

There are 4 types of cycles used in MCU interface of RA8875, please refer to Table 5-1 for detail. The programming or reading of the registers in RA8875 is composed by the cycles. RA8875 includes a status register and tens of instruction registers. The status register is read only and can be read by "Status Read" cycle. The instruction registers, that is used to program almost functions, can be programmed by "Command Write" cycle and "Data Write" cycle. The "Command Write" cycle sets the register number to program, and the "Data Write" cycle set the data of the register. When reading the specific instruction registers, MCU asserts a "Data read" cycle following the "Command Write cycle". The "Command Write" cycle sets the register number to program, and the "Data Read" cycle read the data of the register. The instruction registers are classified to 15 categories as Table 5-2, most of which are readable/writable. All of the registers will be illustrated in the following sections.

Table 5-1 : MCU Cycle Type

| Cycle Type    | RW# | RS | Description                                                                            |

|---------------|-----|----|----------------------------------------------------------------------------------------|

| Command Write | 0   | 1  | Register number write cycle                                                            |

| Status Read   | 1   | 1  | Status read cycle                                                                      |

| Data Write    | 0   | 0  | Corresponding Register data/Memory data write cycle following the Command Write cycle. |

| Data Read     | 1   | 0  | Corresponding Register data/Memory data read cycle following the Command Write cycle.  |

Table 5-2: The Categories of the Instruction Registers

| No. | Command Registers                  | Address                               |

|-----|------------------------------------|---------------------------------------|

| 1   | System and Configuration Registers | [01h], [02h], [04h],<br>[10h] ~ [1Fh] |

| 2   | LCD Display Control Registers      | [20h] ~ [29h]                         |

| 3   | Active Window Setting Registers    | [30h] ~ [3Fh]                         |

| 4   | Cursor Setting Registers           | [40h] ~ [4Eh]                         |

| 5   | BTE Control Registers              | [50h] ~ [67h]                         |

| 6   | Touch Panel Control Registers      | [70h] ~ [74h]                         |

| 7   | Graphic Cursor Setting Registers   | [80h] ~ [85h]                         |

| 8   | PLL Setting Registers              | [88h], [89h]                          |

| 9   | PWM Control Registers              | [8Ah] ~ [8Eh]                         |

| 10  | Drawing Control Registers          | [90h] ~ [ACh]                         |

| 11  | DMA Control Registers              | [B0h] ~ [BFh]                         |

| 12  | KEY & IO Control Registers         | [C0h] ~ [C7h]                         |

| 13  | Floating Window Control Registers  | [D0h] ~ [DBh]                         |

| 14  | Serial Flash Control Registers     | [E0h] ~ [E2h]                         |

| 15  | Interrupt Control Registers        | [F0h] ~ [F1h]                         |

The registers function description is listed below, for each register, a register name and register number is described upper each register function table. Each register contains up-to 8 bits data. In the register function table, detail description, default value and access attribute (RO: Read only, WO: Write only, RW: Read-able and Write-able) are described.

#### 5-1 Status Register

#### Status Register (STSR)

| Bit | Description                                                                                                                                                                                                                      | Default | Access |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | Memory Read/Write Busy (Include Font Write Busy) 0 : No Memory Read/Write event. 1 : Memory Read/Write busy.                                                                                                                     | 0       | RO     |

| 6   | BTE Busy 0: BTE is done or idle. 1: BTE is busy.                                                                                                                                                                                 | 0       | RO     |

| 5   | Touch Panel Event Detected 0: Touch Panel is not touched. 1: Touch Panel is touched. This bit comes from the TP controller ADET signal directly and not de-bounced. It's suggested to check the validation for multiple polling. | 0       | RO     |

| 4   | Sleep Mode Status 0: RA8875 in Normal mode. 1: RA8875 in Sleep mode.                                                                                                                                                             | 0       | RO     |

| 3-1 | N/A                                                                                                                                                                                                                              | 0       | RO     |

| 0   | Serial Flash/ROM Busy Serial Flash/ROM busy status at Direct Access Mode. 0: idle 1: busy                                                                                                                                        | 0       | RO     |

Note: "RO" means read only.

# 5-2 System & Configuration Registers

#### REG[01h] Power and Display Control Register (PWRR)

| Bit | Description                                                                                                                                                                                                                                                                                                        | Default | Access |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | LCD Display Off 0 : Display off. 1 : Display on.                                                                                                                                                                                                                                                                   | 0       | RW     |

| 6-2 | NA                                                                                                                                                                                                                                                                                                                 | 0       | RO     |

| 1   | Sleep Mode 0: Normal mode. 1: Sleep mode.  Note: 1. There are 3 ways to wake up from sleep mode: Touch Panel wake up, Key Scan wake up, Software wake up. 2. When using IIC, this function is not supported. 3. When using SPI, it has its particular steps to use this function, refer to section 6-1-2-3 please. | 0       | RW     |

| 0   | Software Reset 0 : No action. 1 : Software Reset.  Note: The bit must be set to 1 and then set to 0 to complete a software reset.                                                                                                                                                                                  | 0       | WO     |

#### REG[02h] Memory Read/Write Command (MRWC)

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                     | Default | Access |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-0 | Write Function: Memory Write Data  Data to write in memory corresponding to the setting of MWCR1[3:2]. Continuous data write cycle can be accepted in bulk data write case.  Read Function: Memory Read Data  Data to read from memory corresponding to the setting of MWCR1[3:2]. Continuous data read cycle can be accepted in bulk data read case. Note that the first data read cycle is dummy read and need to be ignored. | +       | RW     |

#### REG[04h] Pixel Clock Setting Register (PCSR)

| Bit | Description                                                                                                                                                                                                                                             | Default | Access |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | PCLK Inversion 0: PDAT is fetched at PCLK rising edge. 1: PDAT is fetched at PCLK falling edge.                                                                                                                                                         | 0       | RW     |

| 6-2 | NA                                                                                                                                                                                                                                                      | 0       | RO     |

| 1-0 | PCLK Period Setting Pixel clock (PCLK) period setting. 00b: PCLK period = System Clock period. 01b: PCLK period = 2 times of System Clock period. 10b: PCLK period = 4 times of System Clock period. 11b: PCLK period = 8 times of System Clock period. | 0       | RW     |

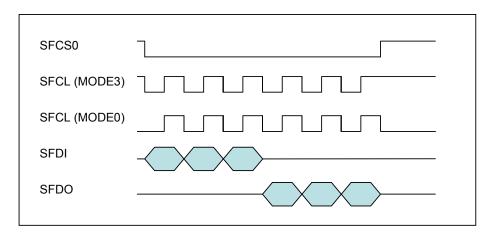

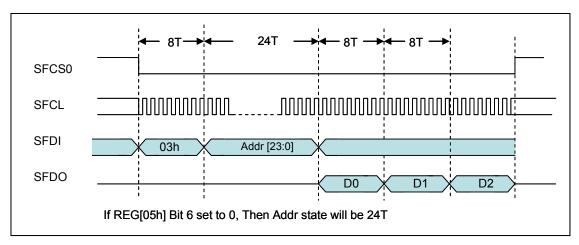

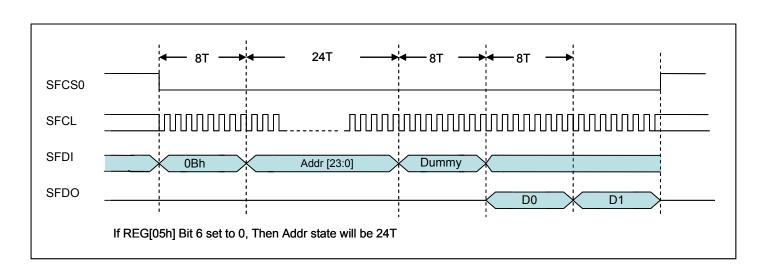

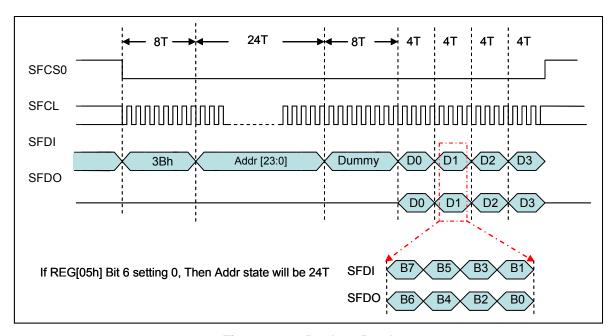

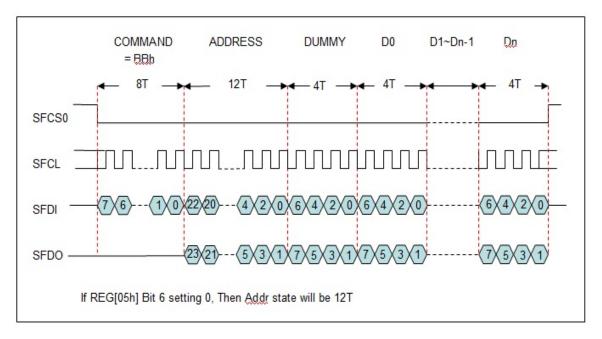

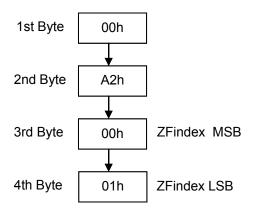

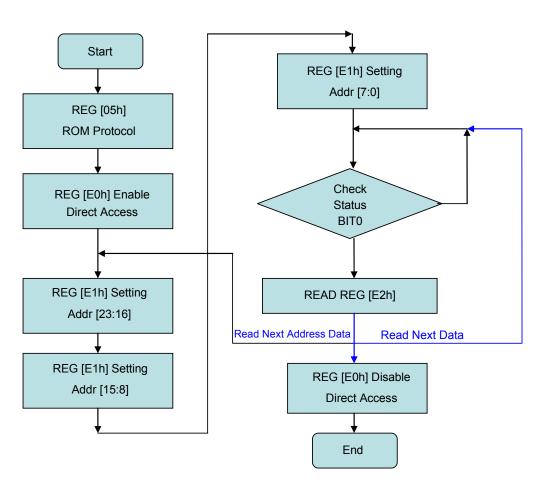

## REG[05h] Serial Flash/ROM Configuration Register (SROC)

| Bit | Description                                                                                                            | Default | Access |

|-----|------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | Serial Flash/ROM I/F # Select  0: Serial Flash/ROM 0 I/F is selected.  1: Serial Flash/ROM 1 I/F is selected.          | 0       | RW     |

| 6   | Serial Flash/ROM Address Mode 0: 24 bits address mode This bit must set to 0 for serial flash.                         | 0       | RW     |

| 5   | Serial Flash/ROM Waveform Mode<br>Mode 0.<br>Mode 3.                                                                   | 0       | RW     |

| 4-3 | Serial Flash /ROM Read Cycle 00b: 4 bus → no dummy cycle 01b: 5 bus →1 byte dummy cycle 1Xb: 6 bus →2 byte dummy cycle | 0       | RW     |

| 2   | Serial Flash /ROM Access Mode 0: Font mode 1: DMA mode                                                                 | 0       | RW     |

| 1-0 | Serial Flash /ROM I/F Data Latch Mode Select 0Xb: Single Mode 10b: Dual Mode 0. 11b: Dual Mode 1.                      | 0       | RW     |

#### REG[06h] Serial Flash/ROM CLK Setting Register(SFCLR)

| Bit | Description                                                                                                                                                                                                                                                                           | Default | Access |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-2 | NA                                                                                                                                                                                                                                                                                    | 0       | RO     |

| 1-0 | Serial Flash/ROM Clock Frequency Setting  0xb: SFCL frequency = System clock frequency  (When DMA enable and Color depth = 256 color  SFCL frequency = System clock frequency /2)  10b: SFCL frequency = System clock frequency / 2  11b: SFCL frequency = System clock frequency / 4 | 0       | RW     |

#### **REG[10h] System Configuration Register (SYSR)**

| Bit | Description                                                                                            | Default | Access |

|-----|--------------------------------------------------------------------------------------------------------|---------|--------|

| 7-4 | N/A                                                                                                    | 0       | RO     |

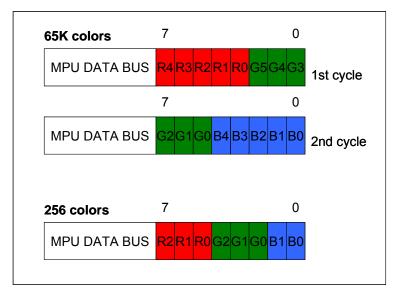

| 3-2 | Color Depth Setting 00b: 8-bpp generic TFT, i.e. 256 colors. 1xb: 16-bpp generic TFT, i.e. 65K colors. | 0       | RW     |

| 1-0 | MCUIF Selection 00b: 8-bit MCU Interface. 1xb: 16-bit MCU Interface.                                   | 0       | RW     |

#### REG[12h] GPI

| Bit | Description                                                                                            | Default | Access |

|-----|--------------------------------------------------------------------------------------------------------|---------|--------|

| 7-5 | NA                                                                                                     | 0       | RO     |

| 4-0 | GPI[4:0] : General Purpose Input.  KEY_EN = 0: General Purpose Input from pin KIN[4:0]  KEY_EN = 1: NC | NA      | RO     |

Note: KEY\_EN: REG[C0h] bit 7

#### REG[13h] GPO

| Bit | Description                                                                                      | Default | Access |

|-----|--------------------------------------------------------------------------------------------------|---------|--------|

| 7-4 | NA                                                                                               | 0       | RO     |

| 3-0 | GPO[3:0] : General Purpose Output KEY_EN = 0: General Purpose Output to KOUT[3:0] KEY_EN = 1: NC | 0       | RW     |

Note: KEY\_EN: REG[C0h] bit 7

#### **REG[14h] LCD Horizontal Display Width Register (HDWR)**

| Bit | Description                                                                                                                                                                                 | Default | Access |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | NA                                                                                                                                                                                          | 0       | RO     |

| 6-0 | Horizontal Display Width Setting Bit[6:0] The register specifies the LCD panel horizontal display width in the unit of 8 pixels resolution. Horizontal display width(pixels) = (HDWR + 1)x8 | 0       | RW     |

*Note :* HDWR must be set less than 64h because that the maximum horizontal display width is 800 pixels.

#### **REG[15h] Horizontal Non-Display Period Fine Tuning Option Register (HNDFTR)**

| Bit | Description                                                                                                                                                                                                            | Default | Access |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | DE Polarity 0 : high active. 1 : low active.                                                                                                                                                                           | 0       | RW     |

| 6-4 | NA                                                                                                                                                                                                                     | 0       | RO     |

| 3-0 | Horizontal Non-Display Period Fine Tuning(HNDFT) [3:0] This register specifies the fine tuning for horizontal non-display period; it is used to support the SYNC mode panel. Each level of this modulation is 2-pixel. | 0       | RW     |

#### **REG[16h] LCD Horizontal Non-Display Period Register (HNDR)**

| Bit | Description                                                                                                                                                                     | Default | Access |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-5 | NA                                                                                                                                                                              | 0       | RO     |

| 4-0 | Horizontal Non-Display Period(HNDP) Bit[4:0] This register specifies the horizontal non-display period. Horizontal Non-Display Period (pixels) =(HNDR + 1)x8+(HNDFTR/2+1)x2 + 2 | 0       | RW     |

#### **REG[17h] HSYNC Start Position Register (HSTR)**

| Bit | Description                                                                                                                                                                                     | Default | Access |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-5 | NA                                                                                                                                                                                              | 0       | RO     |

| 4-0 | HSYNC Start Position[4:0]  The starting position from the end of display area to the beginning of HSYNC. Each level of this modulation is 8-pixel.  HSYNC Start Position(pixels) = (HSTR + 1)x8 | 0       | RW     |

#### **REG[18h] HSYNC Pulse Width Register (HPWR)**

| Bit | Description                                                                                     | Default | Access |

|-----|-------------------------------------------------------------------------------------------------|---------|--------|

| 7   | HSYNC Polarity 0 : Low active. 1 : High active.                                                 | 0       | RW     |

| 6-5 | NA                                                                                              | 0       | RO     |

| 4-0 | HSYNC Pulse Width(HPW) [4:0] The period width of HSYNC. HSYNC Pulse Width(pixels) = (HPW + 1)x8 | 0       | RW     |

#### REG[19h] LCD Vertical Display Height Register (VDHR0)

| Bit | Description                                                               | Default | Access |

|-----|---------------------------------------------------------------------------|---------|--------|

| 7-0 | Vertical Display Height Bit[7:0] Vertical Display Height(Line) = VDHR + 1 | 0       | RW     |

#### **REG[1Ah] LCD Vertical Display Height Register0 (VDHR1)**

| Bit | Description                                                             | Default | Access |

|-----|-------------------------------------------------------------------------|---------|--------|

| 7-1 | NA                                                                      | 0       | RO     |

| 0   | Vertical Display Height Bit[8] Vertical Display Height(Line) = VDHR + 1 | 0       | RW     |

Note: The VDHR must be set less than 1E0h, because the maximum vertical display height is 480.

#### REG[1Bh] LCD Vertical Non-Display Period Register (VNDR0)

| I | Bit | Description                                                                         | Default | Access |

|---|-----|-------------------------------------------------------------------------------------|---------|--------|

| I | 7-0 | Vertical Non-Display Period Bit[7:0] Vertical Non-Display Period(Line) = (VNDR + 1) | 0       | RW     |

#### **REG[1Ch] LCD Vertical Non-Display Period Register (VNDR1)**

| Bit | Description                                                                       | Default | Access |

|-----|-----------------------------------------------------------------------------------|---------|--------|

| 7-1 | NA                                                                                | 0       | RO     |

| 0   | Vertical Non-Display Period Bit[8] Vertical Non-Display Period(Line) = (VNDR + 1) | 0       | RW     |

#### **REG[1Dh] VSYNC Start Position Register (VSTR0)**

| Bit | Description                                                                                                                                     | Default | Access |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-0 | VSYNC Start Position[7:0] The starting position from the end of display area to the beginning of VSYNC. VSYNC Start Position(Line) = (VSTR + 1) | 0       | RW     |

#### **REG[1Eh] VSYNC Start Position Register (VSTR1)**

| Bit | Description                                                                                                                          | Default | Access |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-1 | NA                                                                                                                                   | 0       | RO     |

| 0   | VSYNC Start Position[8] The starting from the end of display area to the beginning of VSYNC. VSYNC Start Position(Line) = (VSTR + 1) | 0       | RW     |

## **REG[1Fh] VSYNC Pulse Width Register (VPWR)**

| Bit | Description                                                                                    | Default | Access |

|-----|------------------------------------------------------------------------------------------------|---------|--------|

| 7   | VSYNC Polarity 0 : Low active. 1 : High active.                                                | 0       | RW     |

| 6-0 | VSYNC Pulse Width[6:0] The pulse width of VSYNC in lines. VSYNC Pulse Width(Line) = (VPWR + 1) | 0       | RW     |

# 5-3 LCD Display Control Registers

REG[20h] Display Configuration Register (DPCR)

| Bit | Description                                                                                             | Default | Access |

|-----|---------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | Layer Setting Control 0 : One layer configuration is selected. 1 : Two layers configuration is selected | 0       | RW     |

| 6-4 | NA                                                                                                      | 0       | RO     |

| 3   | HDIR Horizontal Scan Direction, for n = SEG number. 0 : SEG0 to SEG(n-1). 1 : SEG(n-1) to SEG0.         | 0       | RW     |

| 2   | VDIR  Vertical Scan direction, for n = COM number 0: COM0 to COM(n-1) 1: COM(n-1) to COM0               | 0       | RW     |

| 1-0 | NA                                                                                                      | 0       | RO     |

**REG[21h] Font Control Register 0 (FNCR0)**

| Bit | Description                                                                                                                                                                                                                                                                                                                                            | Default | Access |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7   | CGRAM/CGROM Font Selection Bit in Text Mode  0 : CGROM font is selected.  1 : CGRAM font is selected.  Note:  1. The bit is used to select the bit-map source when text-mode is active(REG[40h] bit 7 is 1), when CGRAM is writing(REG[41h] bit 3-2 =01b), the bit must be set as "0".  2. When CGRAM font is select, REG[21h] bit 5 must be set as 1. | 0       | RW     |

| 6   | NA                                                                                                                                                                                                                                                                                                                                                     | 0       | RO     |

| 5   | External/Internal CGROM Selection Bit 0: Internal CGROM is selected.(REG[2Fh] must be set 00h) 1: External CGROM is selected. (REG[2Eh] bit6 &bit7 must be set 0)                                                                                                                                                                                      | 0       | RW     |

| 4-2 | NA                                                                                                                                                                                                                                                                                                                                                     | 0       | RO     |

| 1-0 | Font Selection for internal CGROM  When FNCR0 B7 = 0 and B5 = 0, Internal CGROM supports the 8x16 character sets with the standard coding of ISO/IEC 8859-1~4, which supports English and most of European country languages.  00b: ISO/IEC 8859-1.  01b: ISO/IEC 8859-2.  10b: ISO/IEC 8859-3.  11b: ISO/IEC 8859-4.                                  | 0       | RW     |

#### REG[22h] Font Control Register1 (FNCR1)

| Bit | Description                                                                               | Default | Access |

|-----|-------------------------------------------------------------------------------------------|---------|--------|

| 7   | Full Alignment Selection Bit 0 : Full alignment is disable. 1 : Full alignment is enable. | 0       | RW     |

| 6   | Font Transparency 0 : Font with background color. 1 : Font with background transparency.  | 0       | RW     |

| 5   | NA                                                                                        | 0       | RO     |

| 4   | Font Rotation 0 : Normal. 1 : 90 degree display.                                          | 0       | RW     |

| 3-2 | Horizontal Font Enlargement 00b: X1. 01b: X2. 10b: X3. 11b: X4.                           | 0       | RW     |

| 1-0 | Vertical Font Enlargement 00b: X1. 01b: X2. 10b: X3. 11b: X4.                             | 0       | RW     |

#### REG[23h] CGRAM Select Register (CGSR)

| Bit | Description                                                                                                                                                                                                                                                                                                                                                                            | Default | Access |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-0 | CGRAM No.  The setting of the number of the character in CGRAM. It's used to write the user-defined character bitmap data into CGRAM. 16 continuous data write cycles compete the bitmap writing of a 8x16 character. Note that the MWCR1 bit 3-2 must be set as 01b(CGRAM) first. And more than 16 data write cycles will loop back to the 1 <sup>st</sup> data and cover the bitmap. | 0       | RW     |

#### REG[24h] Horizontal Scroll Offset Register 0 (HOFS0)

| Bit | Description                                                                                                                                                            | Default | Access |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-0 | Horizontal Display Scroll Offset [7:0]  The display offset of the horizontal direction, changing the value will cause the effect of scrolling at horizontal direction. | 0       | RW     |

#### REG[25h] Horizontal Scroll Offset Register 1 (HOFS1)

| Bit | Description                                                                                                                                                             | Default | Access |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-3 | NA                                                                                                                                                                      | 0       | RO     |

| 2-0 | Horizontal Display Scroll Offset [10:8]  The display offset of the horizontal direction, changing the value will cause the effect of scrolling at horizontal direction. | 0       | RW     |

#### REG[26h] Vertical Scroll Offset Register 0 (VOFS0)

| Bit | Description                                                                                                                                                     | Default | Access |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-0 | Vertical Display Scroll Offset [7:0] The display offset of the vertical direction, changing the value will cause the effect of scrolling at vertical direction. | 0       | RW     |

#### REG[27h] Vertical Scroll Offset Register 1 (VOFS1)

| Bit | Description                                                                                                                                                      | Default | Access |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-2 | NA                                                                                                                                                               | 0       | RO     |

| 1-0 | Vertical Display Scroll Offset [9:8]  The display offset of the vertical direction, changing the value will cause the effect of scrolling at vertical direction. | 0       | RW     |

#### **REG[29h] Font Line Distance Setting Register (FLDR)**

| Bit | Description                                                                                                                        | Default | Access |

|-----|------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-5 | NA                                                                                                                                 | 0       | RO     |

| 4-0 | Font Line Distance Setting Setting the font character line distance when setting memory font write cursor auto move. (Unit: pixel) | 0       | RW     |

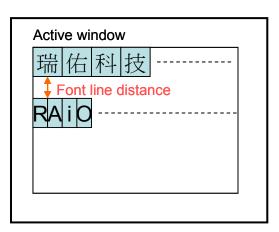

Figure 5-1 : Character Line Distance

#### **REG[2Ah] Font Write Cursor Horizontal Position Register 0 (F\_CURXL)**

| Bit | Description                                                                                                | Default | Access |

|-----|------------------------------------------------------------------------------------------------------------|---------|--------|

| 7-0 | Font Write Cursor Horizontal Position[7:0] The setting of the horizontal cursor position for font writing. | 0       | RW     |

#### REG[2Bh] Font Write Cursor Horizontal Position Register 1 (F\_CURXH)

| - |     |                                                                                                            |         |        |

|---|-----|------------------------------------------------------------------------------------------------------------|---------|--------|

|   | Bit | Description                                                                                                | Default | Access |

| I | 7-2 | NA                                                                                                         | 0       | RO     |

| I | 1-0 | Font Write Cursor Horizontal Position[9:8] The setting of the horizontal cursor position for font writing. | 0       | RW     |

#### REG[2Ch] Font Write Cursor Vertical Position Register 0 (F\_CURYL)

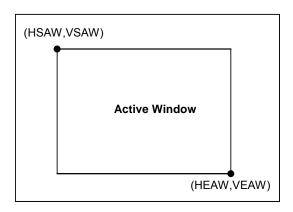

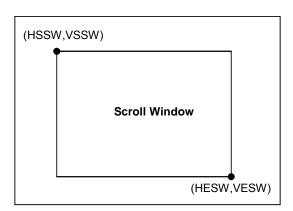

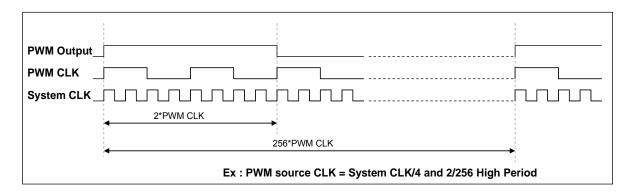

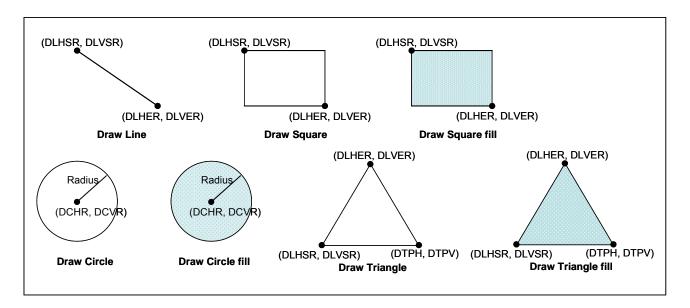

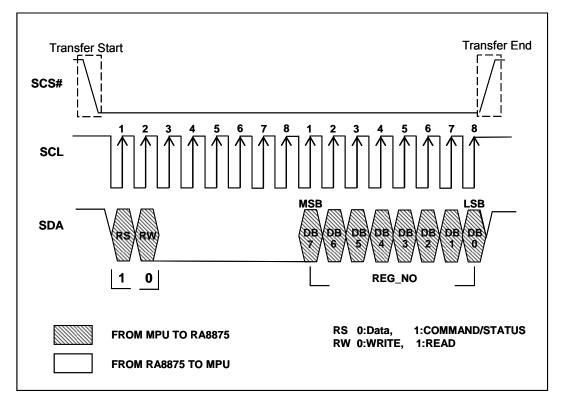

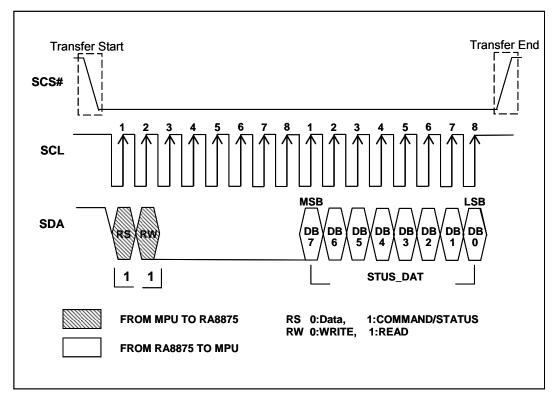

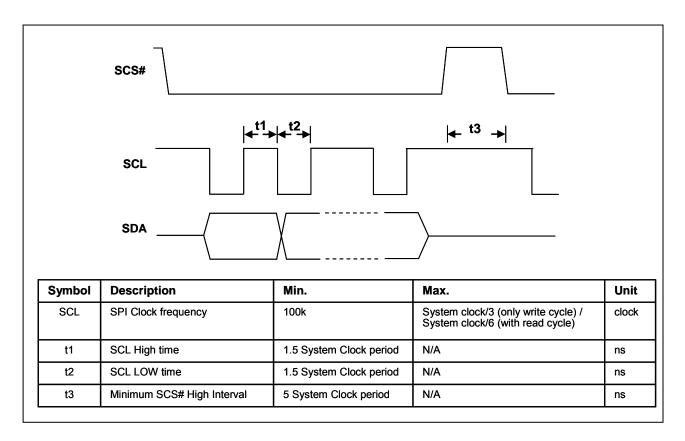

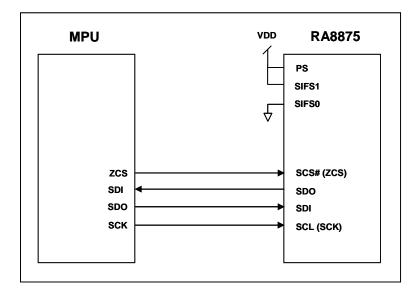

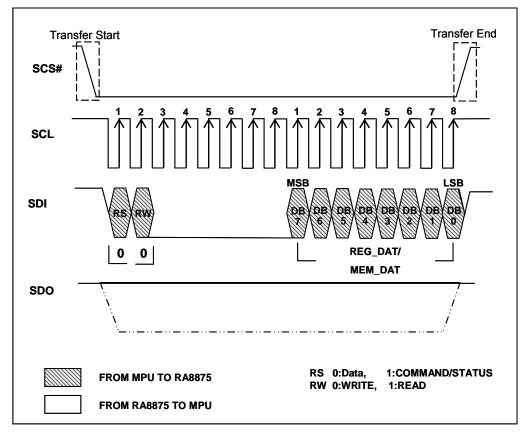

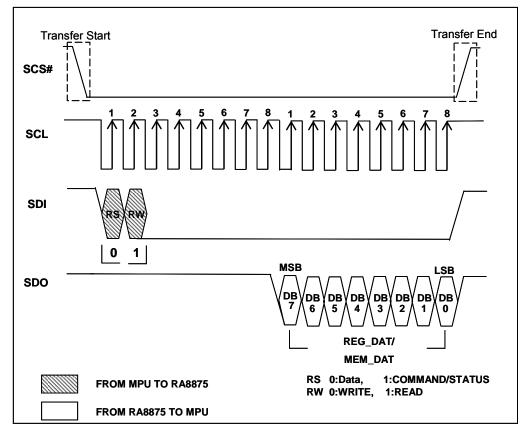

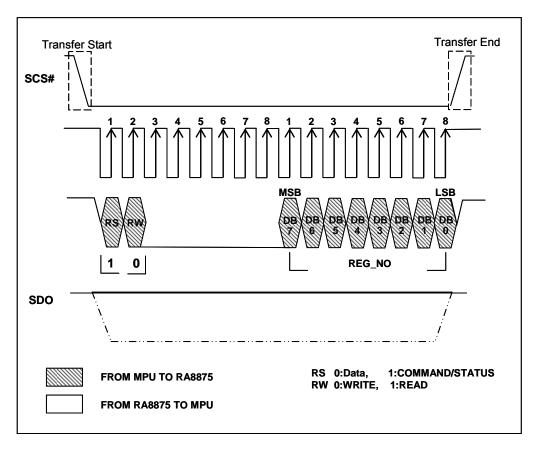

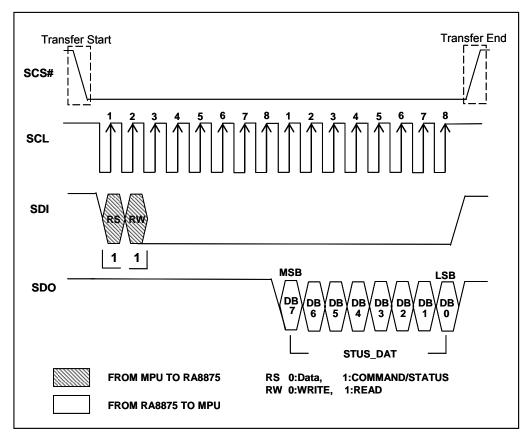

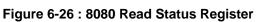

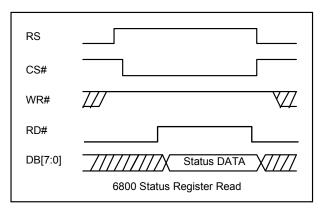

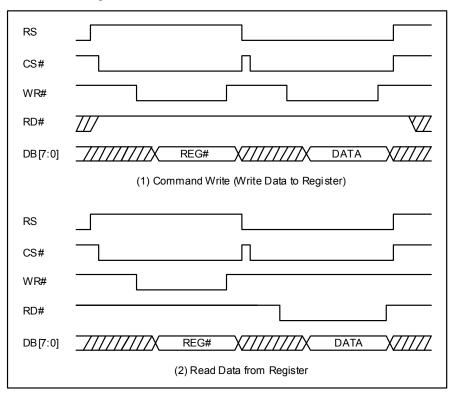

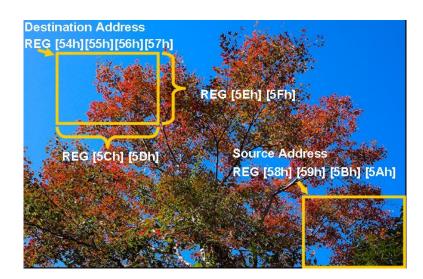

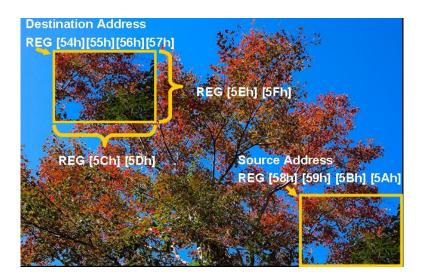

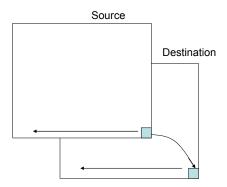

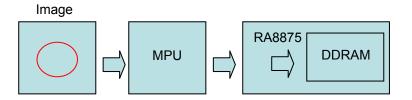

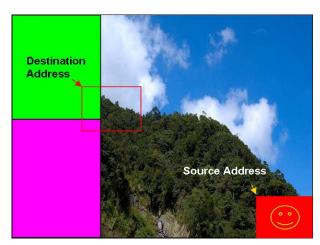

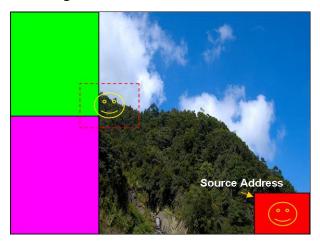

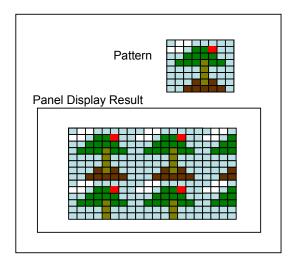

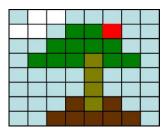

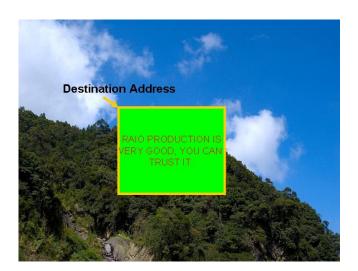

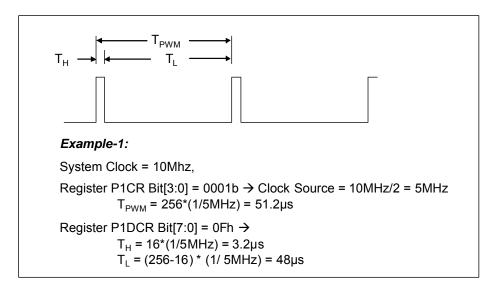

| Bit | Description                                                                                            | Default | Access |